A reduced instruction set computer or RISC architecture is one of the two basic types of instruction set architecture or central processing unit design that uses simpler and fewer instructions that require fewer clock cycles to execute. Processors based on RISC architecture include ARM-based processors such as the A series and M series chips from Apple, including the first-ever Apple M1 system-on-a-chip, and Snapdragon processors from Qualcomm, PowerPC from the AIM Alliance, and SPARC from Oracle Corporation.

Difference With CISC Architecture

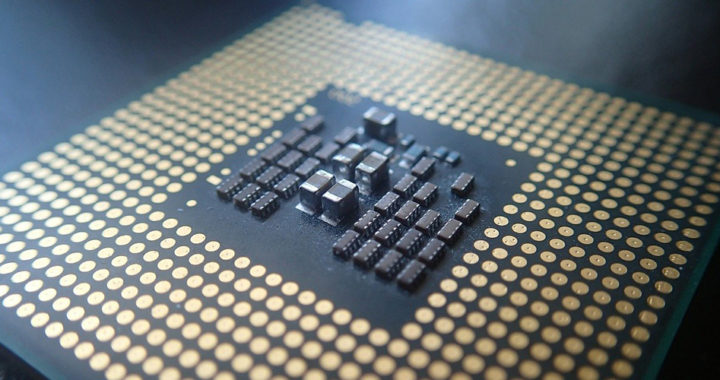

The other basic type of CPU design is complex instruction set computing or CISC architecture that can perform multiple operations per single operation. Some of the notable examples of CPUs based on this design are x86 microprocessors Intel Core and Intel Xeon from Intel, the Athlon and Ryzen lines of microprocessors from AMD, and the once popular Zilog Z80 and Motorola 68000. There are notable differences between RISC and CISC.

RISC architecture uses simpler instructions with one instruction per cycle and fixed instruction sizes. This is in contrast with CISC architecture which uses complex and multi-stage instructions. A simpler explanation of the difference between the two is that RISC tries to perform one thing only per instruction while CISC tries to do more in a single instruction.

Another difference is that RISC processors perform difficult commands by merging them into simpler ones. CISC processors can perform multi-step operations or address modes within one instruction set. The differences between the two also define the differences between x86 processors from Intel and ARM processors from Arm Ltd. There is no superior architecture between the two. Each has its respective advantages and disadvantages.

Advantages of RISC Architecture

The main advantage of RISC centers on the development of processors that are simpler but have excellent performance and efficient power consumption. This is the reason is the reason why devices such as smartphones and tablets have are equipped with chips based on this architecture. Apple has also demonstrated that RISC can also be used in a desktop personal computer environment with performance capabilities that are comparable to mid-range and higher-tier central processing units based on CISC architecture.

Below is a rundown of the advantages of CPU design based on reduced instruction set computer architecture:

1. Compilers of high-level computer language can produce more efficient codes because the architecture has a set of instructions.

2. There is also the time advantage. Each instruction only takes up one cycle. The speed of the operation can be maximized while minimizing the execution time.

3. It also uses a fixed length of instruction, which is easy to pipeline, because specific RISC functions use only a few parameters.

4. A key advantage of RISC architecture is that it requires less number of instruction formats, few numbers of instructions, and few addressing modes.

5. The decoding logic is also simple. Hence, the required transistors are lesser. More general-purpose registers can be fitted into the CPU.

6. Because it lacks complex instruction decoding logic, it supports more registers. This allows less time to load and store values in the memory or cache.

7. From the standpoint of chip designers and manufacturers, RISC processors are easier to design and deploy than CISC processors.

8. It also has a lower per-chip cost because the architecture requires smaller components. Less chip space is used due to the reduced instruction set.

9. Another notable advantage of RISC architecture is that most of the resulting processors are more energy-efficient than CISC-based ones.

Disadvantages of RISC Architecture

The central disadvantage of RISC rests on the fact that processors based on this architecture tend to require more instructions to perform certain complex operations compared to counterpart processors based on CISC. This can translate to larger program sizes and increased memory bandwidth requirements. Reducing the instruction set also shifts the burden of development from hardware to software. The architecture can also struggle in handling certain classes of software applications that heavily depend on complex instructions.

Below is a rundown of the disadvantages of CPU design based on reduced instruction set computer architecture:

1. A notable drawback of RISC architecture is that the performance of the processor depends on the programmer or software developer.

2. The time advantage has a disadvantage. Compilers need to break down high-level instructions into many simpler instructions.

3. Rearranging a CISC code to a RISC code increases the code size. The quality of this code will depend on the compiler and instruction set of the machine.

4. From the standpoint of developers, developing programs for this architecture requires more effort when compared to developing for CISC.

5. The simplicity of a processor based on a reduced instruction set computer puts a lot of stress on the software or application.

6. Feeding instructions require high-speed memory systems. Processors based on this architecture require large memory caches.

7. Of course, it is important to note that the full advantages of RISC still depend on the specific architecture and its deployment.

FURTHER READINGS AND REFERENCES

- Ibrahim, D. 2015. “Microcomputer Systems.” In PIC32 Microcontrollers and the Digilent ChipKIT. Elsevier. DOI: 1016/b978-0-08-099934-0.00001-6

- Koo, K., Rho, G. S., Kwon, W. H., Park, J., and Chang, N. 1998. Architectural Design of a RISC Processor for Programmable Logic Controllers. Journal of Systems Architecture. 44(5): 311-325. DOI: 1016/s1383-7621(97)00011-8

- Stallings, W. 1988. “Reduced Instruction Set Computer Architecture. Proceedings of the IEEE. 76(1): 38-55. DOI: 1109/5.3287